差分振蕩器驅(qū)動自偏置差分輸入

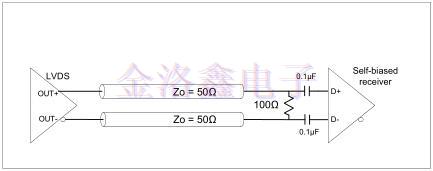

可輸出差分信號的差分晶振是近年來比較熱門的頻率元件之一,LVDS和LVPECL這兩種輸出模式,可降低產(chǎn)品周圍噪聲,和減低相位抖動,實現(xiàn)低功耗.許多差分接收器具有片上DC偏置電路和/或終端網(wǎng)絡(luò).在這種情況下,振蕩器輸出應(yīng)為交流耦合.如果需要外部偏置,則應(yīng)根據(jù)接收器設(shè)備的數(shù)據(jù)表進(jìn)行設(shè)計.LVDS或LVPECL振蕩器可用于驅(qū)動自偏置差分輸入.LVDS輸出需要更少的無源元件和更低的運(yùn)行功率.如果700mV的LVDS擺幅足以用于接收器,則最好使用LVDS石英晶體振蕩器.圖18顯示了LVDS振蕩器與自偏置差分接收器的接口.

圖18:LVDS驅(qū)動器與具有內(nèi)部端接和偏置的自偏置差分接收器的連接

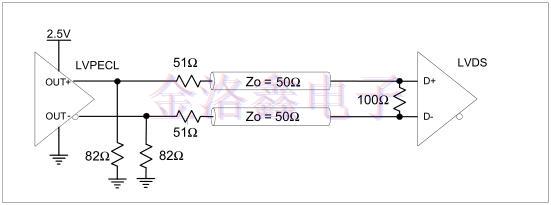

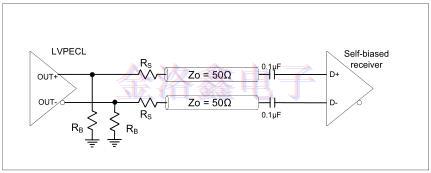

LVPECL輸出可在接收器處產(chǎn)生高達(dá)1.6V的差分?jǐn)[幅.圖19示出了用于將LVPECL差分輸出晶振連接到自偏置差分接收器的示意圖.電阻RS在負(fù)載側(cè)產(chǎn)生一個帶終端的分壓器.可以通過選擇RS值來設(shè)置接收器輸入上的電壓擺動.RB為LVPECL驅(qū)動器提供直流偏置電流,其值可以從公式1計算得出.請注意,接收器將看到RS+50Ω的有效終端電阻值.

圖19:LVPECL驅(qū)動器與具有內(nèi)部端接和偏置的自偏置差分接收器的連接

為了保持信號完整性,RS和RB應(yīng)放置在傳輸線之前,盡可能靠近晶振.負(fù)載側(cè)終端網(wǎng)絡(luò)應(yīng)盡可能靠近接收器輸入.

使用LVPECL驅(qū)動器驅(qū)動LVDS接收器

LVDS接收器可以用LVPECL時鐘信號驅(qū)動.這需要使用終端技術(shù),將接收器側(cè)的信號置于LVDS信令要求之內(nèi).信號共模電壓和信號幅度是必須滿足的主要規(guī)格.為滿足LVDS規(guī)范,LVPECL信號幅度必須從1.6V降至0.75V.LVPECL驅(qū)動器的共模電壓取決于電源電壓,對于2.5V VDD,它與LVDS共模電壓相匹配.終端允許為具有2.5VLVPECL驅(qū)動器的LVDS接收器提供時鐘,如圖20所示.

圖20:將LVPECL驅(qū)動器與2.5V VDD連接到LVDS接收器

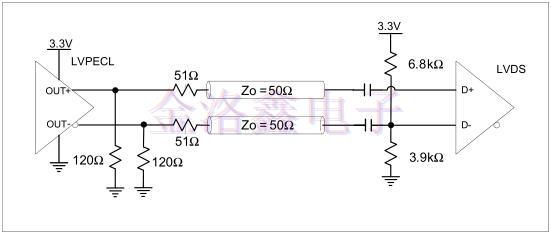

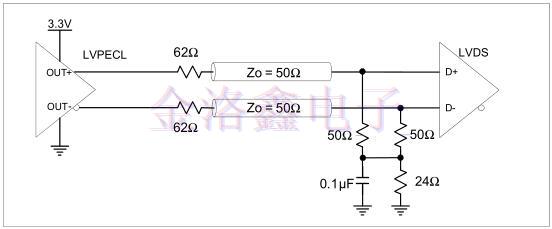

在3.3V VDD的情況下,LVPECL驅(qū)動器和LVDS接收器的共模電壓是不同的.圖21建議使用串聯(lián)電阻和Y端接來連接LVPECL驅(qū)動器和LVDS接收器.

圖21:將LVPECL驅(qū)動器與3.3V VDD連接至LVDS接收器

如果接收器具有片內(nèi)匹配,則建議使用交流耦合,如圖22所示.共模由電阻分壓器設(shè)置.由于差分石英晶振等效電阻太高而不會導(dǎo)致正輸入和負(fù)輸入之間的不平衡,因此只有一個輸入有偏差.

圖22:將LVPECL驅(qū)動器與3.3V VDD連接到具有內(nèi)部端接的LVDS接收器

“推薦閱讀”

【責(zé)任編輯】:金洛鑫版權(quán)所有:http://www.jftz888.com轉(zhuǎn)載請注明出處

相關(guān)新聞動態(tài)

- 瑞薩半導(dǎo)體R-CarGen5驅(qū)動SDV技術(shù)創(chuàng)新的新引擎

- Renesas瑞薩新品推出物聯(lián)網(wǎng)與智能家居的雙功能微控制器

- 瑪居禮HM系列晶振醫(yī)療設(shè)備小型化的可靠時鐘解決方案

- Skyworks超低抖動時鐘緩沖器領(lǐng)域的新標(biāo)準(zhǔn)開創(chuàng)者

- Suntsu松圖VCXO壓控差分晶振電子設(shè)備的頻率魔法師

- QuartzCom專門從事自家生產(chǎn)的TCXO及VC-TCXO產(chǎn)品的制造

- Skyworks與Xilinx利用新推出的C波段頻譜推動了5G技術(shù)的發(fā)展

- SiTime解鎖導(dǎo)航航空航天與國防領(lǐng)域的精密時間密碼

- 解鎖KYOCERA京瓷晶振VCXO壓控差分晶振電子世界的頻率奧秘

- Raltron拉隆晶振為醫(yī)療設(shè)備制造商注入強(qiáng)勁動力

手機(jī)版

手機(jī)版